Highly Integrated Chips: Super-Brains for the IoT Age

Electronic devices are becoming continually smaller, more flat and multifunctional and their “inner life”, the microelectronic systems, along with them – thanks to 3D integration.

Related Vendors

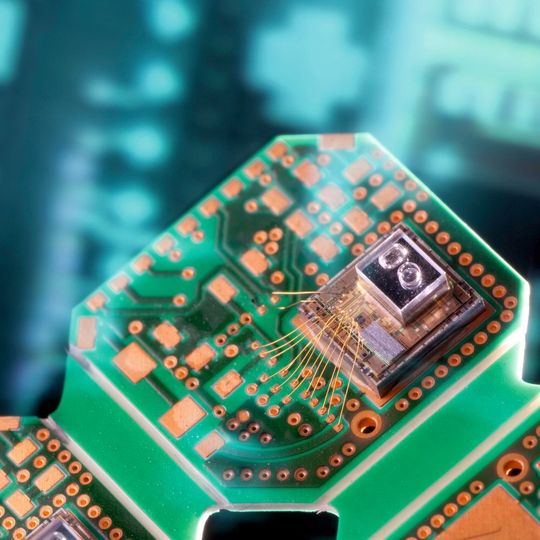

Further miniaturization of electronic devices would not be possible without key technologies like 3D integration. The ability to interconnect heterogeneous components into one single microelectronic system is becoming even more crucial now: It enables highly integrated, smart sensor systems needed e.g. for the Internet of things.

Many of today’s chips show such complex functionalities that they could also be considered as mini-computers: ultra-miniaturized electronic “brains” – following the big European research project “e-Brains” (www.e-brains.org) which are also equipped with sensors, the “sense organs” of things. This is enabled by technologies like high-performant 3D integration, where heterogeneous microelectronic components are stacked on top of one another and connected by electrical through-via-wiring into a highly integrated microelectronic system.

As Peter Ramm and his team from the Fraunhofer Research Institution for Microsystems and Solid State Technologies EMFT started their research activities on 3D integration of microelectronic systems 30 years ago, they were considered as exotics. Meanwhile, this has changed dramatically: 3D integration is established as a key technology to make microelectronic systems smaller, at the same time increasing their performance. The principle of 3D integration can be described very simply: The, in many cases heterogeneous, components of a chip are stacked on top of one another and vertically connected by electrical through via wiring to a single circuit (IC).

Evolutionary Process Since the 80's

From its beginning in the 80´s until today the technology has gone through a big evolutionary process. Basically four different bonding technologies have been established since then – Peter Ramm’s Munich team – especially Armin Klumpp and Josef Weber – conducting pioneer work in the field of 3D integration and deploying all of them.

In the beginning of the 90´s, the Fraunhofer researchers started to use the so-called dielectric bonding. Thereby the wafers are mechanically connected through an oxide layer. The vertical electric through-via-wirings (Through Silicon Vias, TSV) are implemented in a further step. The problem with this method are the comparatively high bonding temperatures, which have a negative impact on lifetime and reliability of the device. “Ideally the bonding temperature should not be much higher than the temperatures the device will be exposed to when it is in use”, Peter Ramm says. One alternative is the method of adhesive bonding, where the substrates are connected with the help of an adhesive. Although this method requires only relatively low temperatures, it has disadvantages as well: The TSVs have to be etched through the complete stacked assembly, including the adhesion layer, and filled with a metallic compound – a complex and expensive procedure.

A real “milestone” was set with the development and application of metal bonding: This method uses the fact that some metal systems like copper-copper or copper-tin are very suitable to connect wafers in a robust and high-quality way. “But the real key feature is that the components can be connected mechanically as well as electrically in one step. This allows for a very simple 3D integration of the chips, using cost-efficient wafer processes”, says Peter Ramm.

Thus, the time-consuming and costly procedure of through-contacting the wafer stacks is no longer required. Based on the metal bonding method, Fraunhofer EMFT researchers developed the so-called SLID-bonding (solid-liquid interdiffusion) in cooperation with colleagues from Infineon. In this technology a low-melting solder layer between two high-melting metals is heated up above its melting point, causing the atoms of the higher melting metal layer, which is still solid at the bonding temperature (e.g. copper), to diffuse into the liquid metal (e.g. tin) and both layers to connect to an intermetallic compound (e.g. Cu3Sn). The melting point of this compound is at much higher temperatures than the bonding temperature. This guarantees a high mechanical stability of the systems.

(ID:45094057)

:quality(80)/p7i.vogel.de/wcms/59/6c/596cdde662a90ad3295fb67ad7f74737/0131244347v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/40/91/4091929a36bbe16e0e0a5e58b3c46d64/0131194558v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/87/33873af45a622686767b0e597d41e7a3/0130872234v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c8/7e/c87e276b243339dbff4a8eca8f67a55e/0130871216v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c6/20/c620db13d7331aa76791b0742c47a9b3/0131248252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/64/1a64a67b53537b893f5a6509dee97d87/0131192946v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/f3/72f3a2fed9f27d1b33a66f3021eb6ed2/0131192934v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/7e/6a7e738aac81597b04bae84add8a9077/0131141034v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/45/6a45ee92ec1a9e84cffe55964a693b74/0131139927v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/2c/6d2c5ab1d18334052a5f173a99758815/0131084924v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/9a/6b9a2f9d820c458d6518f7d3c0cc990e/0131057985v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ff/37/ff3789529a54269859a36f49352f9ac8/0131245949v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/48/54/48540b44b56da638cbfafa7fb05dd4a2/0131245000v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/e5/b4e5eecb07d3491bde7bf6a22602ab77/0131085753v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/a6/43a69c0b9e26996ab4f3971f202afd82/0131055378v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/64/e964996410967c124c2cf01a8623068e/0130285341v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/1c/39/1c39433f4bb4de2e5e6c5311c3236d09/0130110254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/e1/bee13b8d51a419b9b8f0685e2b9d47bf/0128917673v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/51/7a/517a4e83c5827663b4839f5ddb98f434/0128872953v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b7/68/b76861f18db2d568329cdd966cf23e90/0131083977v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/0e/fa0efd09be99b54318c553d9e8dcb52d/0130922390v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/60/ef/60efa975d1dd123c1afbfb6ccc060461/0130263955v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/62/0762f20b1821ee2724c97989374d6397/0130257651v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/31/7931cc94924b4c2ebc7087e9cec2f801/0130490720v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/cc/6bcc3d26e1c7c74d90a10bc3ca296ae1/0128362351v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/c8/24c84ab6b1bcd24468a87820a07a85aa/0128194707v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/3e/1d3e2788eb37c1e974f36337c8d33cb5/0128191010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/79/7179c77f8bae9e48bf427708573ad6ac/0131057546v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3f/7f/3f7f7542cd5392be0f3074f074a75b36/0131055389v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/26/0e/260ee8cbbc76b6dcaa4d6221ecb44506/0131014543v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/94/0e/940e978ce75be13842063b9c81d5f66e/0130871936v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f8/29/f8298429c1638b949a6f76346f6709c7/0118701710v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/24/07242664ab2b1c7841c9d9d0a127670c/0116045959.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/79/c979a20b32395ddfa93fe7ead90578a0/0108386061.jpeg)

:quality(80)/p7i.vogel.de/wcms/9e/5c/9e5c92d942ed046a27562d6e3d730c92/0103483548.jpeg)

:quality(80)/p7i.vogel.de/wcms/57/da/57da73af9c35d633196afd46348182b2/0130820106v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/20/36/20366ffa57a841882fd165e4dc885c09/0130491929v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d0/f7/d0f7d560dfce37c8371442d5b6120e3c/0130182478v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/77/7c77e24fdcc9e1511e8e711eff161e28/0130175489v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a8/4e/a84e8039a90a5cf4751d01ebcf6ba1a9/0127510172v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/c7/17c703445f134eb3d7ecc7918dda2762/0124596096v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2a/2c/2a2cffc07f51019065387cd63241b5ce/0119463370v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b1/7e/b17ea8c62ccafad1d1fb072d6199bbd6/0118578446.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/69/e0/69e09ddd8aac3/aup-logo.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/101800/101879/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/68/c8/68c815bc8fe81/prominent-logo-300x300.jpeg)

:quality(80)/images.vogel.de/vogelonline/bdb/1341700/1341794/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1341700/1341796/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1341700/1341797/original.jpg)

:quality(80)/p7i.vogel.de/wcms/b0/91/b091a2adbf615d2dc8fba812c3130693/0125912213v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2c/9b/2c9baa308158c7e13cd73a292e3c578b/0126393524v2.jpeg)